# IO50 & IO100 Series VXI Digital I/O Modules

Includes Coverage For: IO50 IO51 IO52 IO53 IO54 IO100 IO110 IO120 IO130

IO140

**User's Manual**

## IO50 / IO100 Series Digital I/O Modules

| Record of Changes |                   |                                                                                                                                                                                                                                                                                                              |            |

|-------------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| Change<br>No.     | Date of<br>Change | Title or<br>Brief Description                                                                                                                                                                                                                                                                                | Entered By |

| Rev. 01           | Apr, 1997         | Original Issue                                                                                                                                                                                                                                                                                               | Factory    |

| Rev. 02           | Jan 10, 2000      | Expanded coverage to include IO50 Series.                                                                                                                                                                                                                                                                    | Factory    |

| Change 1          | Jan 16, 2001      | Corrected driver and receiver data, Appendix A, pg A-1                                                                                                                                                                                                                                                       | Factory    |

| Change 2          | Jun 15, 2001      | Added App/Tech Note section to manual                                                                                                                                                                                                                                                                        | Factory    |

| Change 3          | Oct 29, 2001      | Revised pg 1-4 (specifications); revised tables B-1 and B-2 of Appendix B                                                                                                                                                                                                                                    | Factory    |

| Change 4          | Feb 17, 2004      | Revised pgs 6-7 - 6-13 (Figs 6-2 - 6-8) and pg A-2, changed mating connector data.                                                                                                                                                                                                                           | Factory    |

| Change 5          | Apr 28, 2005      | Changed pg 1-1, Table 1-1. Changed pgs 1-2 and 1-3 (IO53 and IO130), (IO54 and IO140). Changed pg 1-5, table at top of page.<br>Changed pgs 6-9 thru 6-14 (figs 6-4 thru 6-9). Fig D-1, changed from "Connector D (IO130 only)" to "Connector D (IO130-002 only)". Corrected typo errors on pgs D-2 and D-3. | Factory    |

## **\*Proprietary Notice\***

This document, and the technical information contained herein, are proprietary of Interface Technology and shall not, without the express written permission of Interface Technology, be used in any form or part to solicit competitive quotations. The information provided herein may be used for operational purposes only, or for the purpose of incorporation into technical specifications or other documents which specify procurement from Interface Technology

## **\*D**ISCLAIMERS**\***

Interface Technology, Inc. makes no warranty of any kind with regard to this material, including, but not limited to, implied warranties or fitness for a particular use or purpose.

Interface Technology, Inc. shall not be liable for errors contained herein or for incidental or consequential damages in connection with the performance or use of this material.

Interface Technology, Inc. reserves the right to make changes to its products and to the content of this manual without notice.

## Contents

|                        | About This Manual                       |      |

|------------------------|-----------------------------------------|------|

| Chapter 1              | Arrangement of Contents                 | 1-1  |

| General Information    | Applicability                           | 1-1  |

|                        | Supersedure Notice                      | 1-1  |

|                        | Equipment Description                   |      |

|                        | Programming Formats                     |      |

|                        | Autonomous Operation                    |      |

|                        | The IO130 and IO53                      |      |

|                        | The IO54 and IO140                      |      |

|                        | Indicators and Connectors               |      |

|                        | LEDs                                    | 1-3  |

|                        | Connectors                              | 1-3  |

|                        | Specifications                          |      |

|                        | General                                 |      |

| Chapter 2              | Operating Modes                         |      |

| Functional Description | Basic Input/Output Mode                 |      |

|                        | Defined Test Modes                      |      |

|                        | Register Access Mode                    |      |

|                        | Basic Test Mode                         |      |

|                        | Defined Test Mode                       |      |

|                        | Block Handshake Tests                   |      |

|                        | Programmed I/O Handshake Tests          |      |

|                        | Block Timed Tests                       |      |

|                        | Programmed Timed Tests                  |      |

|                        | Memory Emulation test                   |      |

|                        | Register Access Mode                    |      |

|                        | Data Organization and Memory Allocation | 2-13 |

|                        | Vectors                                 |      |

|                        | Fields                                  |      |

|                        | Front Panel Connectors                  |      |

|                        | Data Pins                               |      |

|                        | External Tristate Control Pins          |      |

|                        | Request Handshake Control Pins          |      |

|                        | Acknowledge Handshake Control Pins      |      |

|                        | Power Pins                              | 2-19 |

|                        | VXI/VME Connections                     | 2-19 |

|                        | VME Interrupt Request Connections       |      |

|                        | TTL Trigger Connections                 |      |

|                        |                                         |      |

| Chapter 3   | SCPI Command Syntax                            | 3-1  |

|-------------|------------------------------------------------|------|

| Command Set | Standard Commands for Programmable Instruments | 3-3  |

|             | ABORT                                          | 3-5  |

|             | FIELD                                          |      |

|             | :DEFINE                                        | 3-7  |

|             | :PINASSIGNMENT                                 |      |

|             | :NAME                                          | 3-9  |

|             | :TRISTATE                                      | 3-10 |

|             | :TRISTATE?                                     | 3-11 |

|             | :DELETE                                        | 3-11 |

|             | :CATALOG?                                      | 3-12 |

|             | INITIATE                                       | 3-13 |

|             | :INPUT                                         | 3-14 |

|             | :OUTPUT                                        | 3-15 |

|             | :BLOCK                                         | 3-16 |

|             | TEST                                           | 3-17 |

|             | :DEFINE                                        | 3-18 |

|             | :MEMEMULATION                                  | 3-18 |

|             | :SIZE                                          | 3-19 |

|             | :BLKOUTHANDSHAKE                               |      |

|             | :SIZE                                          |      |

|             | :BLKINHANDSHAKE                                |      |

|             | :SIZE                                          |      |

|             | :BLKOUTTIMED                                   | 3-24 |

|             | :SIZE                                          | 3-25 |

|             | :BLKINTIMED                                    | 3-26 |

|             | :SIZE                                          |      |

|             | :PRGIOHANDSHAKE                                |      |

|             | :PRGIOTIMED                                    |      |

|             | :NAME                                          |      |

|             | :STATUS                                        | 3-31 |

|             | :DELETE                                        |      |

|             | :CATALOG?                                      | 3-32 |

|             | :HANDSHAKE                                     | 3-33 |

|             | :REQUEST                                       | 3-33 |

|             | :INPUT                                         |      |

|             | :INPUT?                                        | 3-35 |

|             | :OUTPUT                                        | 3-36 |

|             | :OUTPUT?                                       |      |

|             | :ACKNOWLEDGE                                   | 3-37 |

|             | :INPUT                                         | 3-38 |

|             | :INPUT?                                        |      |

|             | :OUTPUT                                        |      |

|             | :OUTPUT?                                       |      |

|             | :TIMEOUT                                       |      |

|             | :INPUT                                         |      |

|             |                                                |      |

Interface Technology

|             | 2 15 |

|-------------|------|

| :INPUT?     |      |

| :OUTPUT     |      |

| :OUTPUT?    |      |

| ADDR        |      |

| :ADDR?      |      |

| :FREE?      |      |

| VECTOR      |      |

| :COUNT      |      |

| :DATA       |      |

| :VALUE      |      |

| :VALUE?     |      |

| :RADIX      |      |

| :FIELD      |      |

| SYSTEM      |      |

| :ERROR?     | 3-56 |

| :VERSION?   | 3-57 |

| :FIELD      | 3-58 |

| :FIELD?     | 3-58 |

| :TEST       | 3-59 |

| :TEST?      | 3-59 |

| :LEARN      | 3-60 |

| :LEARN?     | 3-61 |

| :TRISTATE?  | 3-62 |

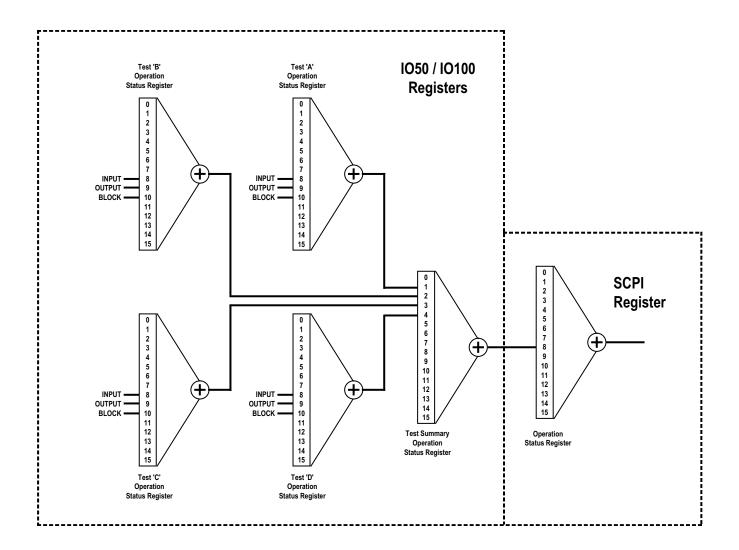

| STATUS      | 3-63 |

| :OPERATION  | 3-66 |

| :EVENT?     | 3-66 |

| :CONDITION? | 3-67 |

| :ENABLE     | 3-68 |

| :ENABLE?    | 3-68 |

| :TEST       | 3-69 |

| :EVENT?     | 3-69 |

| :CONDITION? | 3-70 |

| :ENABLE     | 3-71 |

| :ENABLE?    | 3-71 |

| :ISUMMARY1  | 3-72 |

| :EVENT?     | 3-72 |

| :CONDITION? |      |

| :ENABLE     |      |

| :ENABLE?    |      |

| :ISUMMARY2  |      |

| :EVENT?     |      |

| :CONDITION? |      |

| :ENABLE     |      |

| :ENABLE?    |      |

| ISUMMARY3   |      |

| :EVENT?     |      |

|             | 5-10 |

|                      | :CONDITION?                                          | 3-79  |

|----------------------|------------------------------------------------------|-------|

|                      | :ENABLE                                              | 3-80  |

|                      | :ENABLE?                                             | 3-80  |

|                      | :ISUMMARY4                                           | 3-81  |

|                      | :EVENT?                                              | 3-82  |

|                      | :CONDITION?                                          | 3-82  |

|                      | :ENABLE                                              | 3-83  |

|                      | :ENABLE?                                             | 3-83  |

|                      | BASICMODE                                            | 3-84  |

|                      | :DEFINE                                              | 3-85  |

|                      | :INPUT                                               | 3-86  |

|                      | :OUTPUT                                              | 3-87  |

|                      | :CATALOG?                                            | 3-88  |

|                      | :CLEAR                                               | 3-89  |

|                      | :INPUT?                                              | 3-89  |

|                      | :OUTPUT                                              | 3-90  |

|                      | :OUTPUT?                                             | 3-91  |

|                      | :MODE                                                | 3-92  |

|                      | :SLAVE                                               | 3-93  |

|                      | :GROUP                                               | 3-94  |

|                      | :MASTER                                              | 3-95  |

|                      | :GROUP                                               | 3-96  |

|                      | :STANDALONE                                          | 3-96  |

|                      | :MODE?                                               | 3-97  |

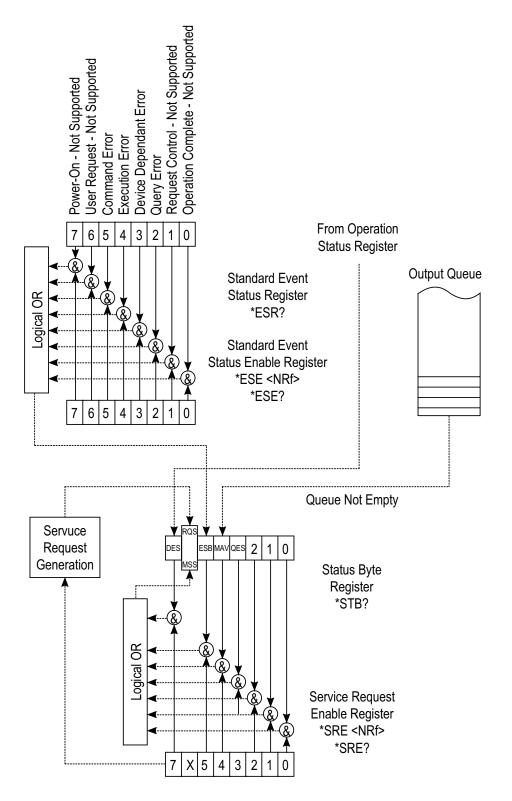

| IEEE 488.2 Mandatory | *CLS                                                 | 3-100 |

| Commands             | *ESE                                                 | 3-100 |

|                      | *ESE?                                                | 3-101 |

|                      | *ESR?                                                | 3-101 |

|                      | *IDN?                                                |       |

|                      | *OPC                                                 |       |

|                      | *OPC?                                                | 3-103 |

|                      | *RCL                                                 | 3-103 |

|                      | *RST                                                 | 3-104 |

|                      | *SAV                                                 | 3-104 |

|                      | *SRE                                                 | 3-105 |

|                      | *SRE?                                                | 3-105 |

|                      | *STB?                                                | 3-106 |

|                      | *TRG                                                 | 3-106 |

|                      | *TST?                                                |       |

|                      | *WAI                                                 | 3-107 |

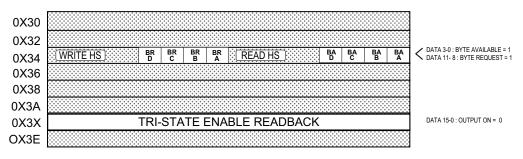

| Chapter 4            | Register Based Operation                             | 4-1   |

| Register Access      | Register Programming Bit Definitions                 |       |

|                      | Data Input and Output Registers (0x20-2F Read/Write) | 4-1   |

Rev. 02

|                      | Control Registers                                              | 4-3   |

|----------------------|----------------------------------------------------------------|-------|

|                      | Output Latch and Trigger 2 Generation (0x30 Write)             |       |

|                      | Input Latch and Trigger 1 Generation (0x31 Write)              |       |

|                      | Request Handshake Polarity Control (0x33 Write)                |       |

|                      | Output Acknowledge Handshake Signal Control (0x34 Write)       |       |

|                      | Output Request Handshake Status (0x34 Read)                    |       |

|                      | Input Acknowledge Handshake Signal Control (0x35 Write)        |       |

|                      | Output Interrupt Mask and Inverted Acknowledge                 |       |

|                      | Control (0x36 Write)                                           | 4-5   |

|                      | Input Interrupt Mask and Inverted Acknowledge                  |       |

|                      | Control (0x37 Write)                                           | 4-5   |

|                      | Output Latch Strobe Select Control (0x38 Write)                |       |

|                      | Input Latch Strobe Select Control (0x39 Write)                 |       |

|                      | Input Latch Strobe Select Control (0x39 Write)                 |       |

|                      | Tristate Polarity (0x3A Write) and Output Control (0x3C Write) |       |

|                      | Tristate Enable Readback (0x3C Read)                           |       |

|                      | Trigger Input/Output Select (0x3F Write)                       |       |

|                      |                                                                |       |

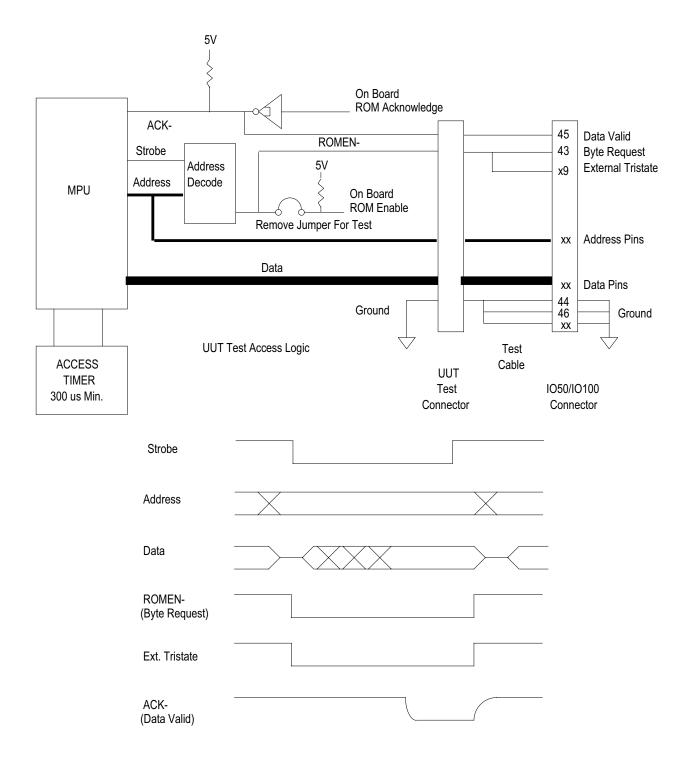

| Chapter 5            | Memory Emulation                                               | 5-1   |

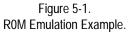

| Applications         | ROM Emulation                                                  | 5-2   |

|                      | RAM Emulation                                                  |       |

|                      | ROM Emulation with Programmed I/O                              |       |

|                      | Techniques for Clocking With Data Pins                         |       |

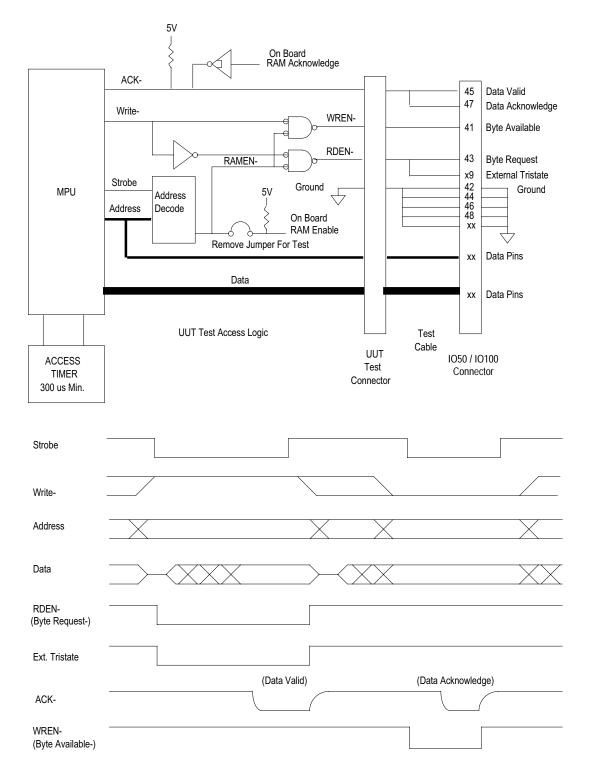

|                      | Output and Input Testing of Memory Devices                     |       |

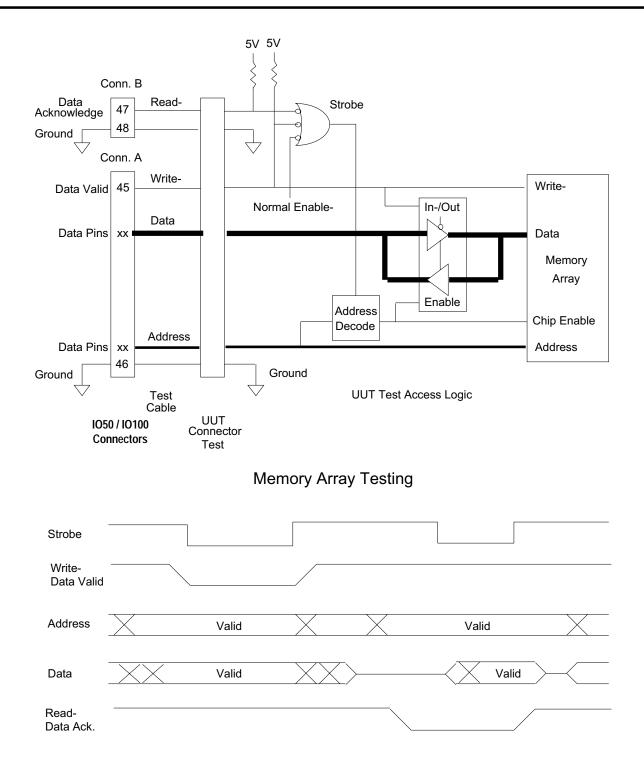

|                      | Testing Memory Mapped I/O Control Logic                        |       |

|                      | Counter or FIFO Testing                                        | 5-13  |

| Chapter 6            | Scope of Chapter                                               | 6-1   |

| Installation         | Unpacking and Inspection                                       |       |

|                      | Installation                                                   |       |

|                      | Logical Addressing                                             |       |

|                      | Slot Dependency                                                |       |

|                      | Calibration                                                    |       |

|                      | Basic Operation                                                |       |

|                      | Self-Test                                                      |       |

|                      | Basicmode I/O                                                  | 6-3   |

|                      | Running and Stopping                                           |       |

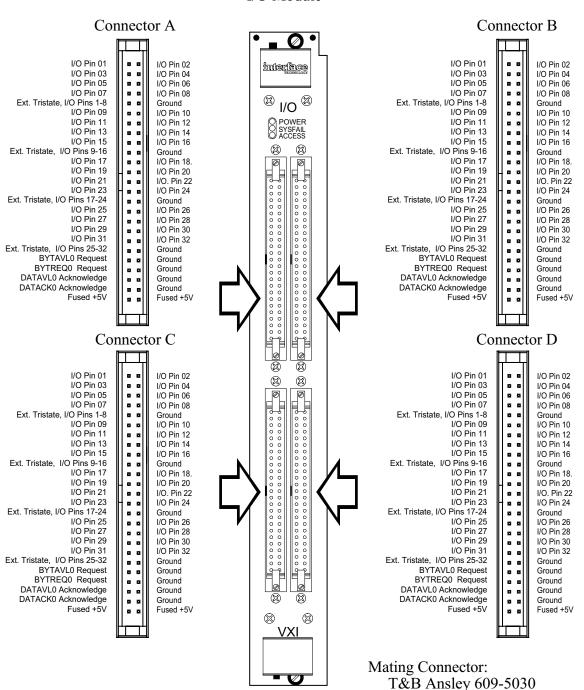

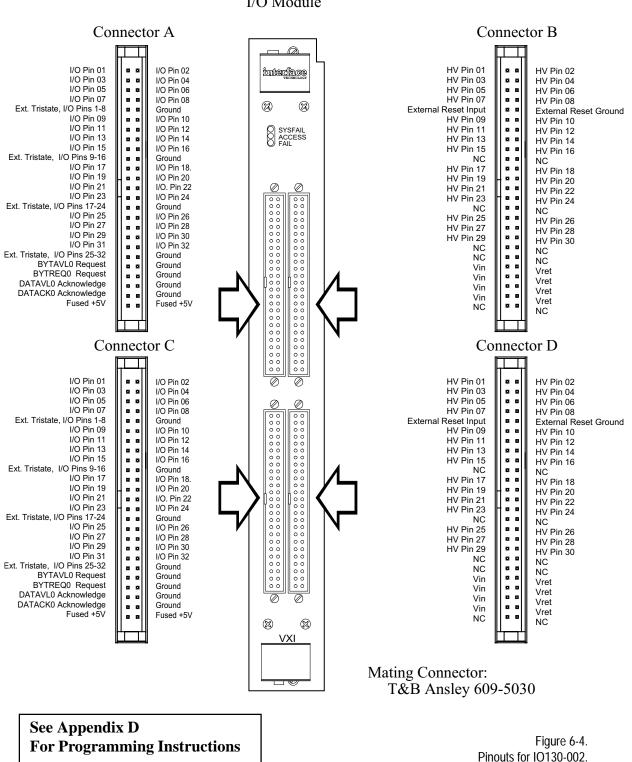

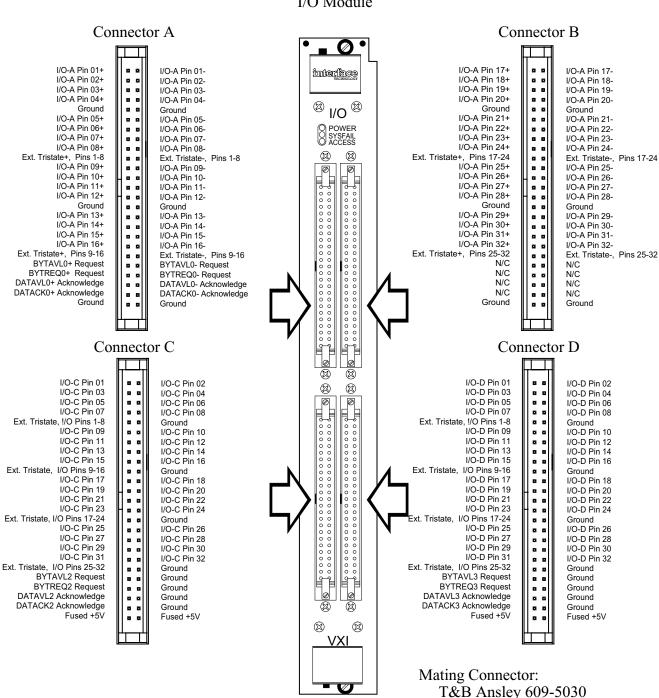

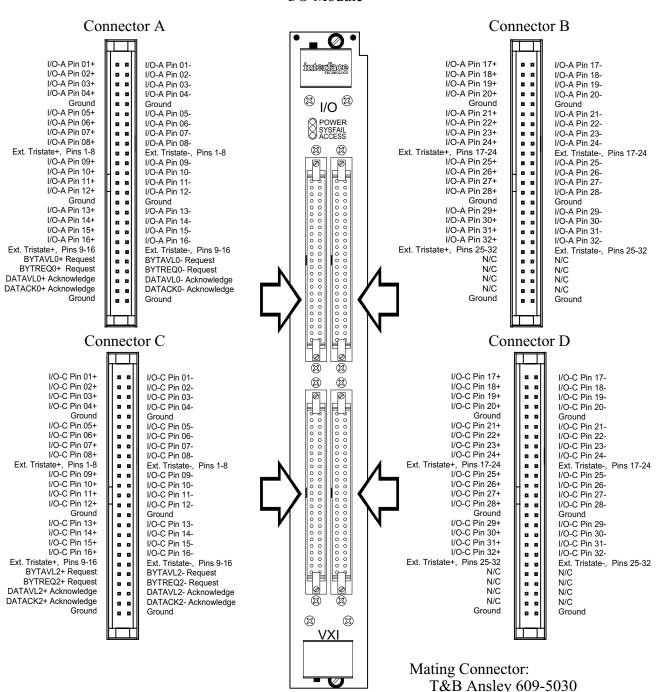

|                      | Pinouts                                                        |       |

| Appendix             |                                                                | A 4   |

| Appendix A           | Specifications                                                 |       |

| Appendix B           | Drivers and Receivers                                          |       |

| Appendix C           | Error Codes                                                    |       |

| Appendix D           | Programming Instructions for High Voltage Switching Option     | . D-I |

| AppNotes & TechNotes | IO50/100-10 Using IO50 and IO100 Backplane Voltages            |       |

Interface Technology

(THIS PAGE INTENTIONALLY LEFT BLANK)

#### C H A P T E R 1

## **General Information**

#### **About This Manual**

This manual provides installation and operation information for the Interface Technology IO50 series and IO100 series Digital I/O Modules. Information contained herein is intended for use by technical personnel involved in the actual installation and operation of the subject modules.

#### Arrangement of Contents

Information contained in this manual is arranged in six chapters, as follows:

- o Chapter 1 General Information

- o Chapter 2 Functional Description

- o Chapter 3 Command Set

- o Chapter 4 Register Access

- o Chapter 5 Applications

- o Chapter 6 Installation and Basic Operation

#### Applicability

The information contained in this manual covers ten equipment configurations, as listed in Table 1-1. Differences, if any, between this equipment and the actual equipment supplied are covered by Difference Data included at the front of this manual.

| Model     | I/O Channels      | Logic Family                         |

|-----------|-------------------|--------------------------------------|

| IO50      | 64                | FTTL                                 |

| IO51      | 64                | ACTTTL/CMOS                          |

| IO52      | 64                | TTL Open Collector                   |

| IO53      | 30 Outputs + 32   | Solid State Relay + FTTL or CMOS I/O |

| IO54      | 32 Diff. I/O      | Differential TTL                     |

| IO100     | 128               | FTTL                                 |

| IO110     | 128               | ACTTTL/CMOS                          |

| IO120     | 128               | TTL Open Collector                   |

| IO130     | 30 Outputs + 96   | Solid State Relay + FTTL or CMOS I/O |

| IO130-002 | 60 Outputs + 64   | Solid State Relay + FTTL or CMOS I/O |

| IO140     | 32 Diff. I/O + 64 | Differential TTL + TTL or CMOS       |

| IO140-002 | 64 Diff. I/O      | Differential TTL                     |

#### Table 1-1. List of Equipment Configurations.

#### **Supersedure Notice**

This manual supersedes Interface Technology IO100 Digital I/O Module User's Manual Rev. A.1.00 in its entirety.

#### Interface Technology

#### **Equipment Description**

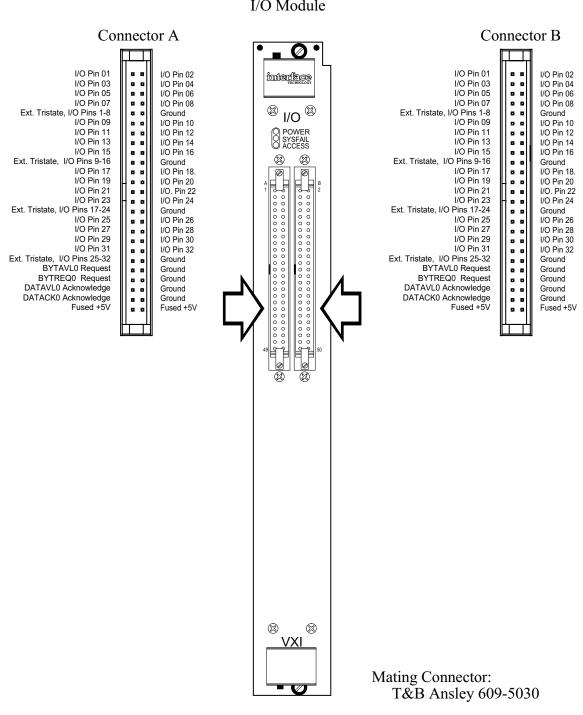

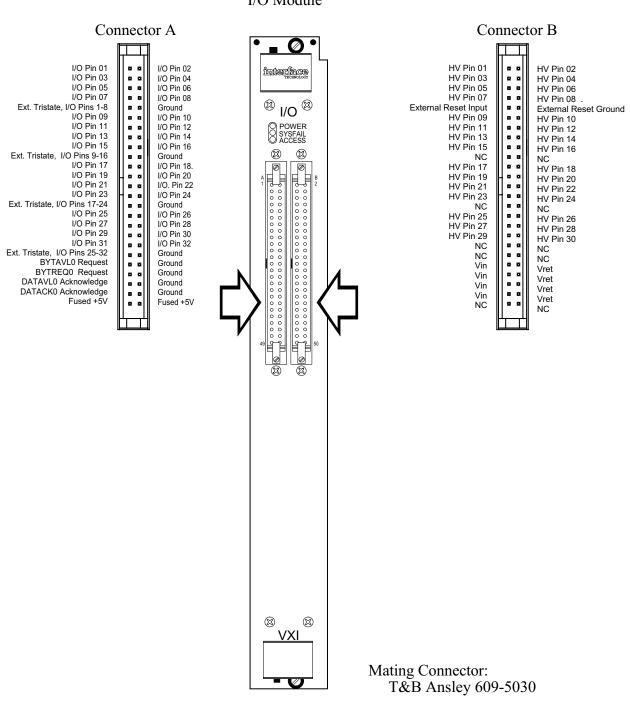

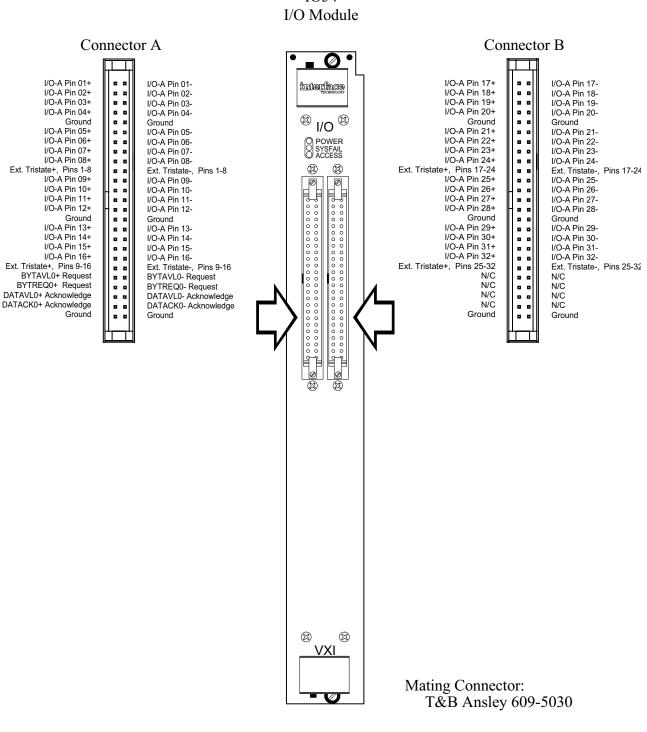

The IO50 and IO100 series of Digital Input/Output modules were developed for use in process control, microprocessor cycle emulation, bus cycle emulation, process simulation, and functional board or circuit test applications. All modules are single slot, C-size VXI modules, with the IO100 series providing up to 128 channels of digital I/O and the IO50 series providing up to 64 channels of digital I/O. Each group of 8 channels may be software configured as either input or output. Tristate control of outputs allow for emulation of bi-directional data and control busses. Four 50-pin IDC connectors are provided on the IO100 series front panel, two on the IO50 series. Each I/O connector provides 32 I/O channels, 4 I/ O handshake strobes, and 4 tristate control/output enable inputs.

**Programming Formats.** All modules use a high level, SCPI-compatible command set for setup and control of I/O channels. They also support VME dual-ported RAM and registers. I/O pins may be programmed by sending high-level commands or with direct, high speed VME read/writes, the same as might be used for register-based instruments. Using this combination of programming formats results in the best of both worlds, high functionality and high speed.

**Autonomous Operation.** Memory emulation and block input or output modes allow autonomous operation from the local microprocessor. Data fields may be programmed from 1-bit to 32-bits wide. Multiple data fields may be defined, allowing I/O pins to be grouped together based on function. Double latching the outputs allows all output channels to transition at the same time, regardless of field size or the number of fields defined. Latching the inputs allows a full 128 bit wide read with a single command (64 channels for the IO50). Utilizing the VXI TTLTRG lines, modules may be linked together for even wider I/O channel groups.

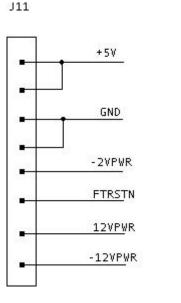

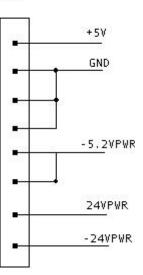

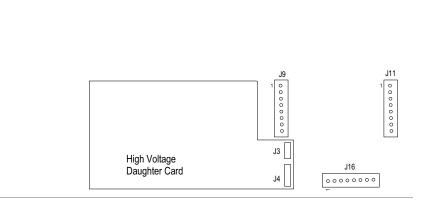

**The IO53 and IO130** modules provide users with 30 optically isolated solid-state relay outputs for applications requiring high voltage outputs. The IO53 provides 30 high voltage output channels and 32 TTL or CMOS I/O channels and the IO130 provides 30 high voltage output channels and 96 TTL or CMOS I/O channels. The relays allow the module to control high voltage applications up to 100 volts, AC or DC. Switched voltages can be either user supplied via the front panel, or selected from +5,  $\pm$  12 and  $\pm$  24 volts available from the VXI backplane. The TTL I/O channels are the same as the IO100 TTL channels described previously.

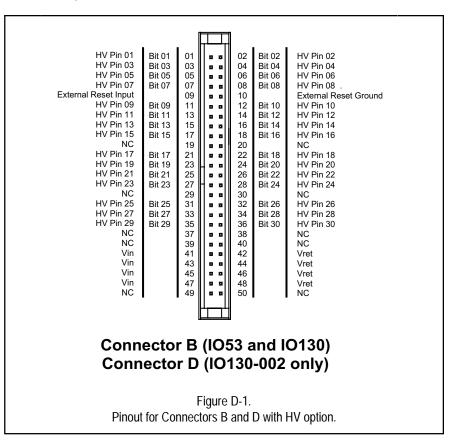

An option for the IO130, the IO130-002, substitutes an additional 30 high voltage output channels for the 32 TTL channels on port/connector "D", providing a total of 60 high voltage outputs and 64 TTL or CMOS I/O channels. Both the IO53 and IO130 modules support external I/O hand-shaking for their TTL or CMOS I/O ports. The handshake I/O pins are used for supplying the external switched voltages on the high voltage ports.

**The IO54 and IO140** modules provide users with differential TTL I/O for applications requiring greater noise immunity and longer cable runs. The IO54 provides 32 Differential TTL I/O channels, each with switchable 100 ohm termination. The IO140 also provides 32 differential I/O channels with switchable 100 ohm terminations, plus an additional 64 TTL or CMOS I/O channels. IO140 TTL channels are the same as the IO100 TTL channels described previously. An option for the IO140, IO140-002, substitutes an additional 32 differential TTL channels on port "B" for the 64 TTL or CMOS channels on ports "B" and "D".

The differential I/O channels meet RS-422-A standard. To accommodate the greater number of signals (a positive/negative signal pair per channel), port B has been eliminated and port A signals mapped to connector A and connector B. An error will be generated if an attempt is made to define a test using port B. For option IO140–002, only ports A and C are valid. Both the IO54 and IO140 modules support external I/O handshaking for their valid ports.

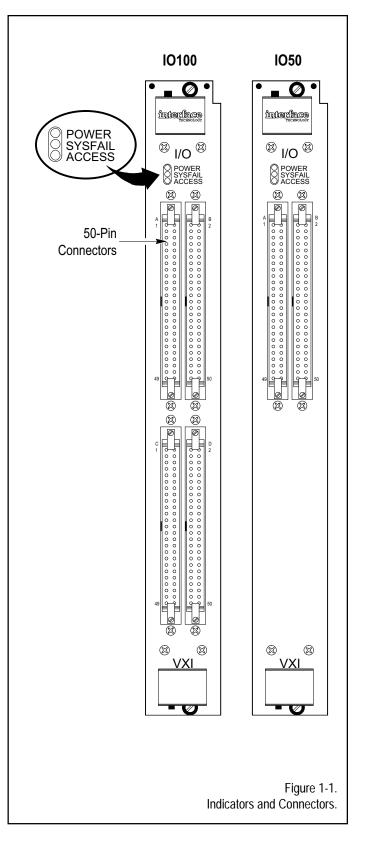

#### Indicators and Connectors

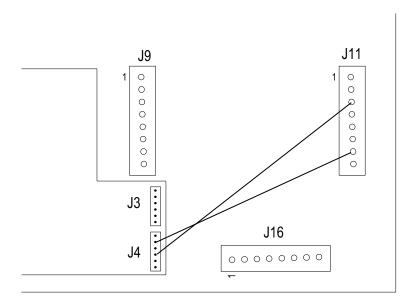

See Fig. 1-1. All the connectors and LEDs for the I/O Module are located on the module front panel.

#### LEDs

There are three LEDs located at the top of the I/O Module front panel.

- o **POWER** (Green) On any time power is applied to the module.

- SYSFAIL (Red) Off during normal operation. During the power-up sequence,

SYSFAIL is lit until completion of internal self test. If SYSFAIL remains lit, a fault exists within the module.

- o **ACCESS** (Yellow) Lit briefly anytime the module is accessed by the VXI bus.

#### CONNECTORS

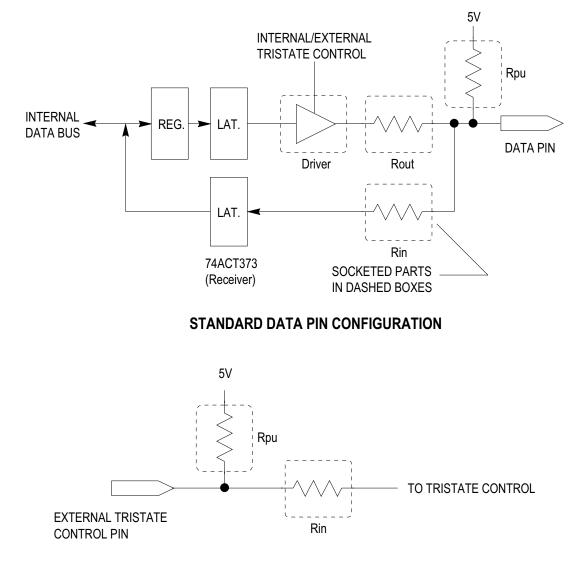

Four 50-pin connectors are provided on the IO100 series, two 50-pin connectors on the IO50 series. Connector location and pin numbering are described in Chapter 6 *Installation*. Each connector has 32 data pins organized as four bytes of 8-bits each. Each byte has internal and external tristate output control.

Other signals on each connector include one pair of request and acknowledge handshake strobe lines for input, another pair for output, one external tristate control for each byte, eight paired ground lines, and two fused 5 volt supply pins.

#### **SPECIFICATIONS\***

| Model     | I/O Channels      | Logic Family                         |

|-----------|-------------------|--------------------------------------|

| 1050      | 64                | FTTL                                 |

| IO51      | 64                | ACTTTL/CMOS                          |

| IO52      | 64                | TTL Open Collector                   |

| IO53      | 30 Outputs + 32   | Solid State Relay + FTTL or CMOS I/O |

| IO54      | 32 Diff. I/O      | Differential TTL                     |

| IO100     | 128               | FTTL                                 |

| IO110     | 128               | ACTTTL/CMOS                          |

| IO120     | 128               | TTL Open Collector                   |

| IO130     | 30 Outputs + 96   | Solid State Relay + FTTL or CMOS I/O |

| IO130-002 | 60 Outputs + 64   | Solid State Relay + FTTL or CMOS I/O |

| IO140     | 32 Diff. I/O + 64 | Differential TTL + TTL or CMOS       |

| IO140-002 | 64 Diff. I/O      | Differential TTL                     |

#### Logic Families:

| FTTL<br>IO100/IO50<br>Skew****<br>Rise/Fall                                                              | Vol* 0.55 V<br>Vil 0.8 V<br>Iol 64 mA<br>15 ns, max.<br>3 ns/3 ns      | Voh**<br>Vih<br>Ioh            | 2.4 V<br>2.0 V<br>-3 mA        |

|----------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|--------------------------------|--------------------------------|

| CMOS<br>IO110/IO51<br>Skew****<br>Rise/Fall                                                              | Vol* 0.5 V<br>Iol 24 mA<br>20 ns, max.<br>4 ns/4 ns                    | Voh**<br>Ioh                   | 3.7 V<br>-24 mA                |

| Open Collector<br>IO120/IO52<br>Skew****<br>Rise/Fall                                                    | Vol* 0.42 V<br>Vil 0.8 V<br>Iol 64 mA<br>20 ns, max.<br>3 ns           | Voh**<br>Vih<br>Ioh***         | 5.0 V<br>2.0 V<br>0.5 mA       |

| Switched<br>IO130/IO53<br>Max Voltage<br>Turn on/off Time<br>On Resistance<br>Isolation<br>Carry Current | 100 V peak A<br>4 ms<br>20 ohm max.<br>Optical, 3750<br>120 mA         |                                |                                |

| Differential TTL<br>IO140/IO54<br>Skew****<br>Rise/Fall                                                  | Vol* 0.50 V<br>Vil 0.8 V<br>Iol 20 mA<br>21 ns, max.<br>14 ns/14 ns (t | Voh**<br>Vih<br>Ioh<br>ypical) | 2.5 V<br>2.0 V<br>-20 mA (max) |

#### Handshake and Control:

(except Switched High Voltage Outputs)

| Byte Available/Request  | Per I/O connector              |

|-------------------------|--------------------------------|

| Data Valid/Acknowledge  | Per I/O connector              |

| Tristate Control Inputs | 1 per byte (except IO120/IO52) |

| Output Enable Inputs    | 1 per byte (IO120/IO52 only)   |

#### **VXI Specifications**

#### Interface Compatibility:

| internate to inpanionit,         | ,.                                                                              |  |

|----------------------------------|---------------------------------------------------------------------------------|--|

| Type<br>VXI Revision             | Message-based, servant only<br>1.3 and 1.4                                      |  |

| Size                             | C-size, single slot                                                             |  |

| Configuration<br>Interrupt Level | Static or Dynamic                                                               |  |

| TTLTRG 0-7<br>two                | Programmable 1-7<br>Input or output, selectable in groups of                    |  |

| Memory                           | A24 RAM, 256K                                                                   |  |

| Power Requirements:              |                                                                                 |  |

| All modules<br>(except IO53/130) | +5 volts, 3.2 A, 16 W typ.                                                      |  |

| IO53 / IO130                     | +5 volts, 3.7 A, 18 W typ.,<br>±12, ±24 volts user selectable                   |  |

| <b>Cooling Requirements</b>      | 5:                                                                              |  |

| Per-slot Average<br>Airflow      | 16 W typical<br>1L / sec @ 0.30 mm water pressure for<br>10° C temperature rise |  |

| Environmental Specifications:    |                                                                                 |  |

| Temperature                      | Storage = $-40^{\circ}$ C to $+75^{\circ}$ C                                    |  |

| Temperature | Storage = $-40^{\circ}$ C to $+75^{\circ}$ C |

|-------------|----------------------------------------------|

|             | Operating = $0^{\circ}$ C to $45^{\circ}$ C  |

| Humidity    | 5% to 95% relative, noncondensing            |

#### **Software Drivers:**

| National Instruments | LabWindows/CVI |

|----------------------|----------------|

|                      |                |

- Maximum voltage at minimum load.

- \*\* Minimum voltage at maximum load.

- \*\*\* Depends on pull-up resistor value.

- \*\*\*\* Channel-to-channel skew. Add 50 ns for channel-to-channel skew across multiple cards.

\*Specifications subject to change without notice.

\*

(THIS PAGE LEFT BLANK INTENTIONALLY)

#### CHAPTER 2

### **Functional Description**

#### General

Both the IO50 and the IO100 (IO50/IO100) are general purpose, parallel, digital interfaces that provide stimulus or receive response from a variety of devices. Each data transfer (stimulus or response) is controlled by the user provided Slot-0 Controller using either message-based commands or direct shared-register access. Several modes of operation allow I/O transfers to be controlled by the local IO50/IO100 processor, or by hand-shake control signals from the UUT (Unit Under Test). The type of output driver and resistive termination can be modified by changing socketed parts within the IO50/IO100 module (refer to Chapter 5, Installation). Data signals are single ended, connected by means of ribbon cable or discrete wiring. Control lines are paired with ground lines to improve transmission reliability over cable runs of up to one meter in length.

**Operating Modes Basic Input/Output Mode.** In its simplest operating mode, the IO50/ IO100 serves as a parallel interface controlled from the user supplied Slot-0 Controller. Typical applications for this mode of operation include process monitoring and control involving slow operating devices such as relays, switch closures, and valve control via I/O module racks. Very wide digital test vectors and responses can be sent and received in this mode.

> **Defined Test Modes**. A more sophisticated level of use is provided by the Defined Test modes of operation. These modes are useful in applications where a more "intelligent" device is sending or receiving data and requires strobe signals to control the transfer. Block data movement can be used to couple asynchronous systems together in the manner of FIFO buffers. Memory emulation functions are provided for aiding in test of microprocessor based devices with limited test point access.

> **Register Access Mode**. Users with unique requirements can control all hardware aspects of the IO50/IO100 using shared access to the VXI Device Dependent registers. This mode provides those users with software development capability with the option of defining their own macro operation commands on their chosen Slot-0 Controller.

#### Basic Test Mode The Basic Test Mode requires minimal setup to produce output or read input on the data pins. Data is transferred when the command is executed without regard to UUT connections to the handshake or external tristate control signals. This mode also offers the option of configuring multiple I/O modules within a single VXI chassis for simultaneous input or output. Any number of the available data pins from 1 to 128 (1 to 64 in the case of the IO50 series) may be used for input or output. Data values transferred will be read or written simultaneously regardless of data "width". Each pin used must be defined as an input or output before data values are sent or received. Pins are defined in byte groups with the following boundaries: 32-25, 24-17, 16-9, and 8-1. The shortened references used for these groups in the command set are: 25, 17, 9, and 1. These values will always define pin groups of exactly eight bits. Pin definition commands may specify multiple bytes or may skip bytes (e.g., A25, A17, A1). Pins defined as outputs will have their output drivers enabled and data specified in the command will appear at the outputs. Even on pins defined as outputs, the current output data may be read back for verification. This is helpful in determining if a shorted or low impedance line is being driven. Output data storage is initialized to zero by hardware reset or VXI soft reset. All data pins are affected with each BASICmode:OUTput command. Outputs which are not specifically set by a command will be zero-filled. For a data field to remain constant throughout a sequence of Basic outputs, it must be referenced in each command. Each pin definition command for output will clear any previously defined output pins, but not affect input pin definition. Input pin definition commands will clear previously defined inputs without affecting outputs. All input and output pins are returned to undefined by the CLEar command. The CATalog? query is provided to allow readback of all currently assigned pins. Note Output drivers are enabled in byte-wide groups so that all pins in the same octet will have their outputs enabled. Be sure that "don't care" pins in an output group are not connected or are connected only to input devices.

An error condition will be generated if an attempt is made to define pins within the same octet as different types (input and output). The best practice in configuring test fixtures is to estimate the required number of inputs and outputs, allowing spares for future use, and round up to the nearest byte boundary before making the UUT wire harness.

Data read back from the defined input pin list will be returned in the order listed in the pin definition command. Users may take advantage of this

|                   | list order control to perform byte swapping of data read from sources with differing byte order conventions. If a data value sent is not wide enough to fill the defined output pin field, bits will be zero filled from most significant down. In this case, the pins specified last in the definition command (right most) will output the available data and the pins specified first (left most) will output zeros. Input commands will return a data value equal in width to the number of defined input pins.                                                                                                                                                                        |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                   | The general procedure for using the Basic Input/Output Mode of operation<br>and the programing sequence, are shown in Chapter 3, Command Set and<br>examples are shown in Chapter 4.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Defined Test Mode | Up to four tests may be defined at any given time, and are designated by<br>the letters A, B, C and D. The letters A, B, C, and D correspond to the<br>independent sets of handshake control signals available on each of the<br>four connectors. A UUT test fixture may use different control signals on<br>each of the connectors, and switch between them by changing the active<br>test. The first test defined after power up, or when all tests have been<br>deleted, becomes the active test. The active test can then be changed by<br>using the SYSTem:TEST command with the desired test letter parameter.<br>Only the handshake signals of the current active test are enabled. |

|                   | There are five Define Test types                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                   | <ol> <li>Block In/Out Handshake</li> <li>Block In/Out Timed</li> <li>Programmed I/O Handshake</li> <li>Programmed I/O Timed</li> <li>Memory Emulation</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                   | Each defined test type provides some unique feature not provided by the other test types. Normally, only one test will be active at any given time. However, provisions have been made to allow Timed I/O Tests to be initiated after a Handshake I/O Test is already running.                                                                                                                                                                                                                                                                                                                                                                                                             |

|                   | The handshake signals provided for data flow control with the UUT are<br>used in some manner by all the defined tests. The timed tests require no<br>requesting handshake from the UUT, but toggle the acknowledge hand-<br>shake with each data value transferred. This provides a strobe for UUTs<br>that might have input or output registers or latches (FIFOs, shift registers,<br>etc.). The handshake type tests will not transfer data until the UUT<br>initiates a request. This allows more intelligent devices to control the<br>flow of data at their own speed (data recorders, display devices, etc.).                                                                       |

|                   | Test operation is started with the INITiate command and can be stopped at<br>any time with the ABORT command. In the case where two tests are<br>running a one time (Memory Emulation and Programmed I/O), the                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

INITiate and ABORT commands act only on the active test, as selected by the SYSTem:TEST command.

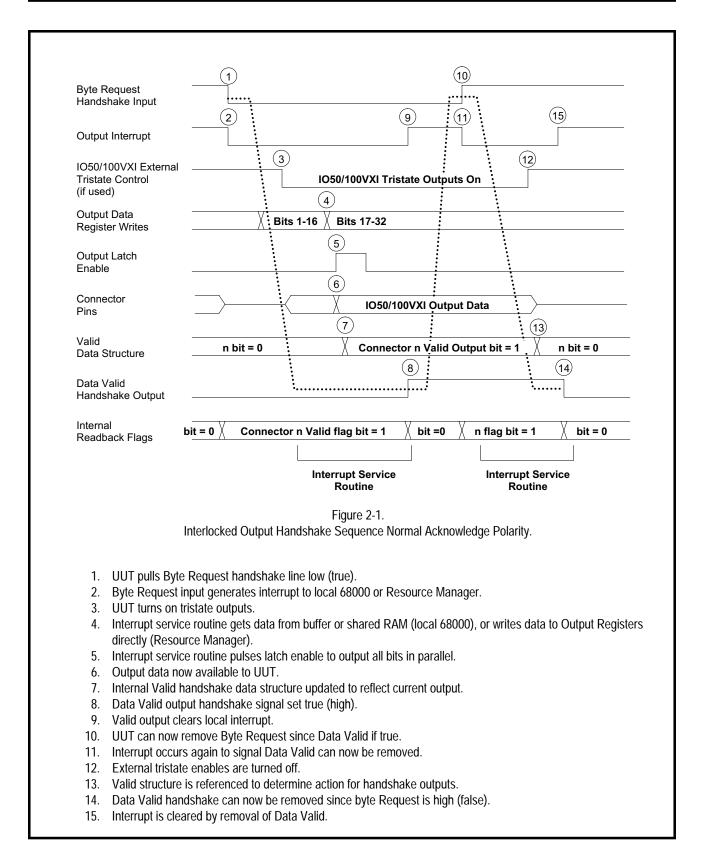

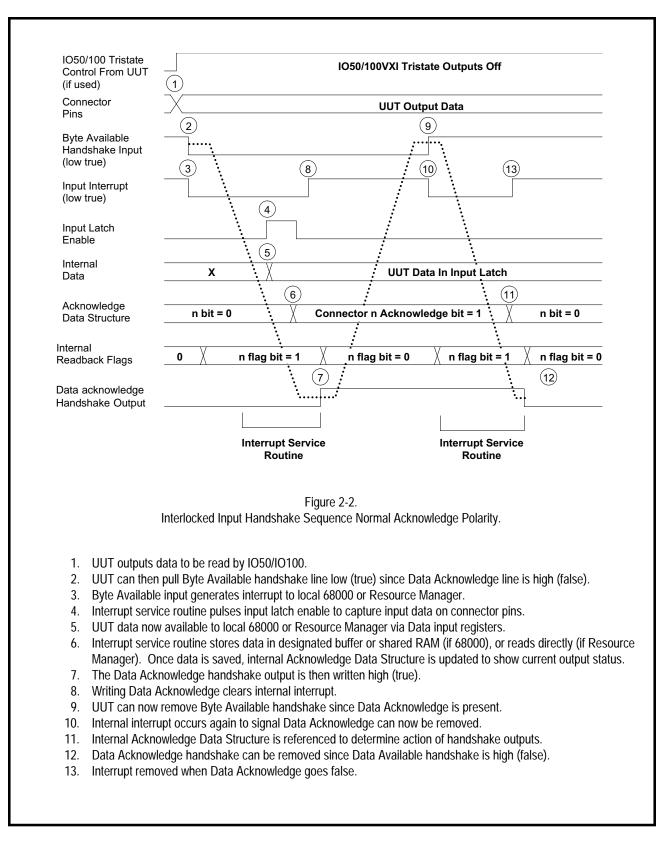

**Block Handshake Tests** Block Handshake type test provide the capability to move a block of data between the IO50/IO100 Shared Memory area and the UUT, with data flow controlled by the UUT. Block Handshake tests are initiated by the user supplied Slot-0 Controller, then performed autonomously by the local 68000 MPU on the IO50/IO100. Once initiated, the Slot-0 need perform no other operation until an end condition occurs (last item is transferred). All input or output operations are controlled by the UUT's use of the handshake lines (see Figs 2-1, 2-2, and 2-3). An interrupt can be sent to the Slot-0 Controller after the last data value has been transferred. The STATUS commands are used to enable this interrupt. Block Handshake tests provide a FIFO-like speed decoupling between the IO50/IO100 and the UUT.

Shared Memory locations are allocated for each block memory test, with separate areas for input and output. Each data vector allocates 16 bytes of shared RAM, allowing access to any bit in the 128 pin array (64 bit pin array in the case of IO50 series) operation, regardless of the actual number of data bits changing, or their position. The rate of transfer is, therefore, independent of the width of the data field being transferred. Shared Memory data values can be accessed by the VECTOR:DATA command or by direct access from the Slot-0 Controller. Once a Handshake Test is started, no other handshake test may be initiated. However, it is possible to start a Timed Test, even if a Handshake Test is already running.

Programmed This test provides single data value input and output with the UUT controlling data flow (see Figs 2-1, 2-2, and 2-3). Data locations for input and I/O Handshake Tests output are separate, much like a full duplex communications peripheral. To perform output, the Slot-0 Controller will first prepare an output data vector. The VECTOR:DATA command can be used, or direct memory access to the vector location in shared memory. The INITIATE:OUT command is then sent to attempt data output. The IO50/IO100 will then wait for an output request on the handshake input from the UUT before transferring data. The TEST:NAME:STATUS? command can be used by the Slot-0 Controller to determine if the data has been transferred. Alternately, the STATUS command can be used to enable an interrupt when the UUT has received the pending data value and is ready for the next. If an attempt is made to send a second data value before the first has been transferred, an error is generated. At any time, the ABORT command may be sent to halt a pending transfer.

> Input operation is similar, with the UUT sending a read request to the IO50/ IO100 when it has data available. If the INITIATE:IN command has been executed, this request will cause data be read to the input vector location. If the input interrupt is enabled, a Slot-0 interrupt is sent after the data has been read. The TEST:NAME:STATUS? command can be used to determine if

any data has been transferred. The Slot-0 Controller may access the input data with the VECTOR:DATA command, or direct read of shared memory.

An acknowledge signal is sent to the UUT at the completion of each data transfer, forming an interlock handshake sequence. For output data, the acknowledge is sent when valid data is available on the IO50/IO100 output pins. For input, the acknowledge handshake is sent when the UUT data has been latched in from the IO50/IO100 input pins.

Shared Memory locations are allocated for Programmed Test with separate areas for input and output. Each data vector allocates 16 bytes of shared RAM, allowing access to any bit in the 128-pin (64-pin for IO50 Series) array. One entire data vector is transferred on each input or output operation, regardless of the actual number of data bits changing, or their position. Shared Memory data values can be accessed by the VECTOR:DATA command or by direct access from the Slot-0 Controller. Once a Handshake Test is started, no other Handshake Test may be initiated. However, it is possible to start a Timed Test even if a Handshake Test is already running.

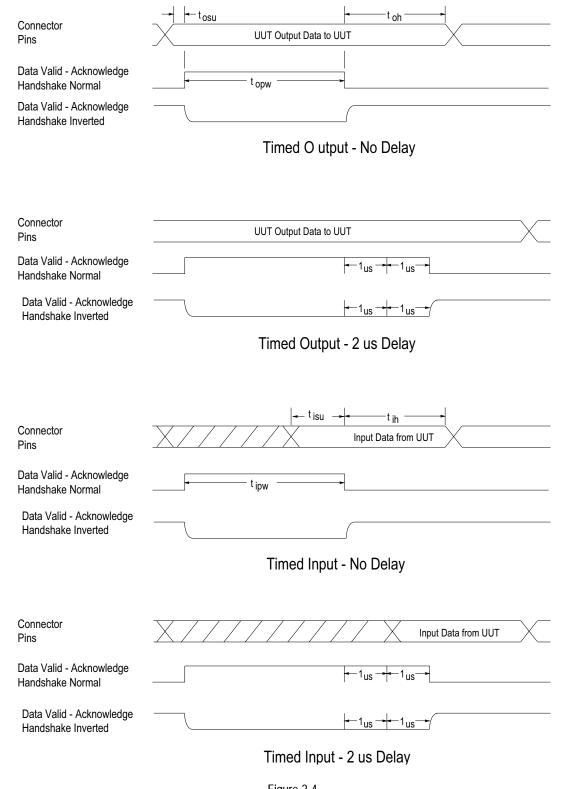

**Block Timed Tests** This test operation provides the capability to move a block of data between the IO50/IO100 shared memory area and the UUT, with data flow at a programmed rate. Block Timed Tests are initiated by the Slot-0 Controller, then performed autonomously by the local 68000 MPU in the IO50/ IO100. Once initiated, the Slot-0 Controller need perform no other operation until an end condition occurs (last item is transferred). All input or output operations are controlled by instruction sequencing on the 68000 MPU (see Fig 2-4). An interrupt can be sent to the Slot-0 Controller after the last data value has been transferred. The STATUS commands are used to enable this interrupt. This test can provide output to UUT devices with clocked or latched input data requirements, but no local intelligence to control data flow. The IO50/IO100 will provide a clocking strobe with each data value output. The TEST:NAME:TIMEOUT command can be used to control the rate of data output and adjust the data setup or hold time in relation to the strobe output.

Shared Memory locations are allocated for each Block Memory Test, with separate areas for input and output. Each data vector allocates 16 bytes of shared RAM, allowing access to any bit in the 128-pin (64-pins in the case of IO50) array. One entire data vector is transferred on each input or output operation, regardless of the actual number of data bits changing, or their positions. The rate of transfer is, therefore, independent of the width of the data field being transferred. Shared Memory data values can be accessed by the VECTOR:DATA command or by direct access from the Slot-0 Controller. Once a Timed Test is started, no other commands will be executed until the test is complete. For this reason, it is not possible to

| Control From UUT                                                                                                                                                                                                                                              | IO50/100VXI Tristate Outputs Off                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (if used)                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Connector                                                                                                                                                                                                                                                     | UUT Output Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Pins                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Byte Available<br>Handshake Input                                                                                                                                                                                                                             | ······································                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| handshake input                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Input Interrupt                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| p.atapt                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Input Latch Control                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Register Data                                                                                                                                                                                                                                                 | X Write 1 X Write 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Input Latch Control                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Register Clock                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Internal                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Data                                                                                                                                                                                                                                                          | X X UUT Data In Input Latch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Acknowledge<br>Data Structure                                                                                                                                                                                                                                 | Initialized to 1 Clear to 0 Set to 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Internal<br>Readback Flags                                                                                                                                                                                                                                    | 0 X Connector n Available flag bit true X 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Reauback Flags                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Data acknowledge                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Handshake Output                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                               | Interrupt Service                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                               | Routine                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                                                                                                                                                                                                               | Routine<br>Figure 2-3.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

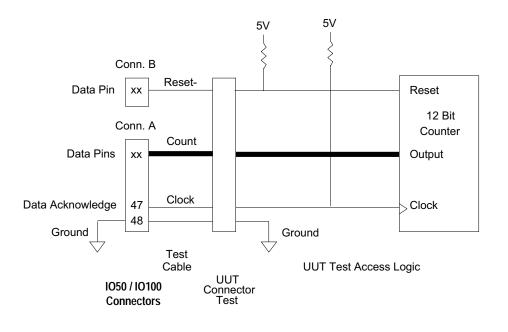

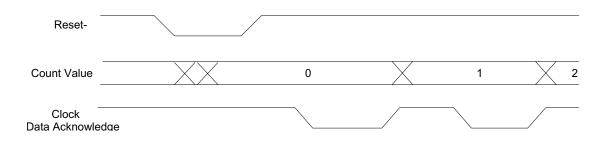

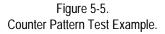

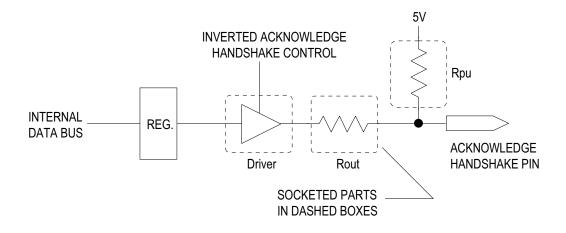

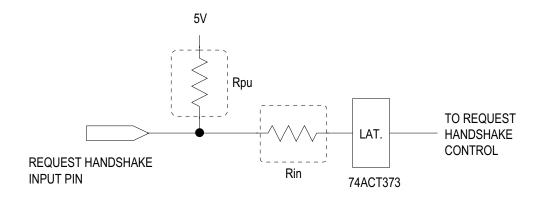

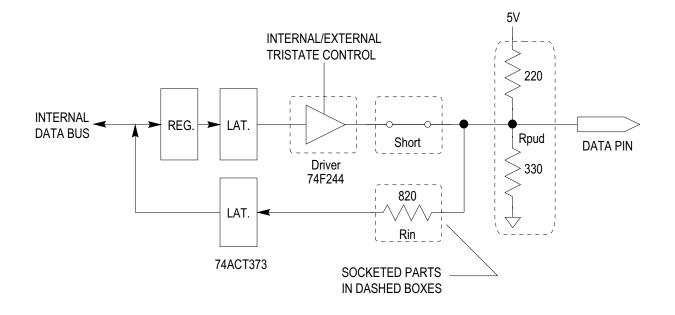

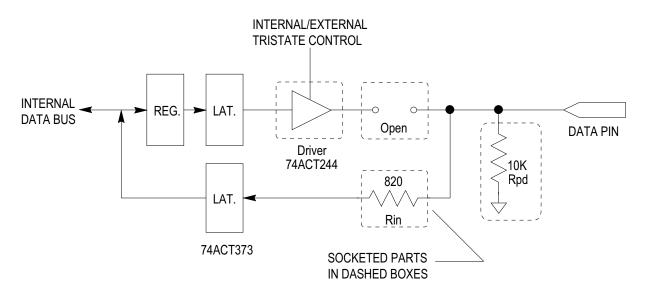

|                                                                                                                                                                                                                                                               | Routine                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |